Simulink Design Verifier utiliza métodos formales para identificar errores de diseño ocultos en modelos. Detecta bloques en el modelo que dan como resultado un desbordamiento de enteros, lógica fallida, infracciones de acceso a arrays y división por cero. Puede verificar formalmente que el diseño cumple con los requisitos funcionales. Por cada error de diseño o infracción de requisitos, se genera un caso de prueba de simulación para la depuración.

Simulink Design Verifier genera casos de prueba para satisfacer los objetivos personalizados y de cobertura de modelos con el fin de ampliar los casos de prueba existentes basados en requisitos. Estos casos de prueba hacen que su modelo cumpla con los objetivos de condición, decisión, condición/decisión modificada (MCDC) y cobertura personalizada. Además de los objetivos de cobertura, puede especificar objetivos de pruebas personalizadas para generar automáticamente casos de prueba basados en requisitos.

El soporte para estándares de la industria está disponible a través de IEC Certification Kit (ISO 26262 y IEC 61508) y DO Qualification Kit (DO-178 y DO-254).

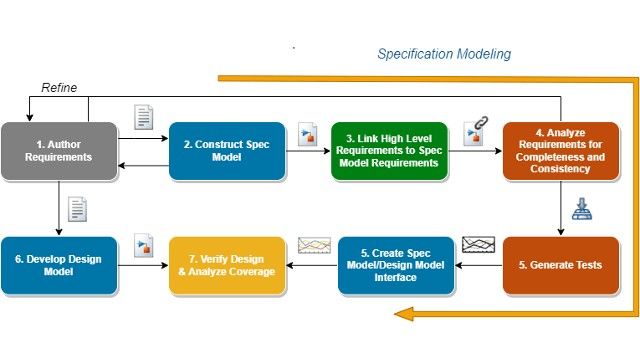

Validación de requisitos

Compruebe la fidelidad y la integridad de los requisitos modelados antes de comenzar a diseñar.

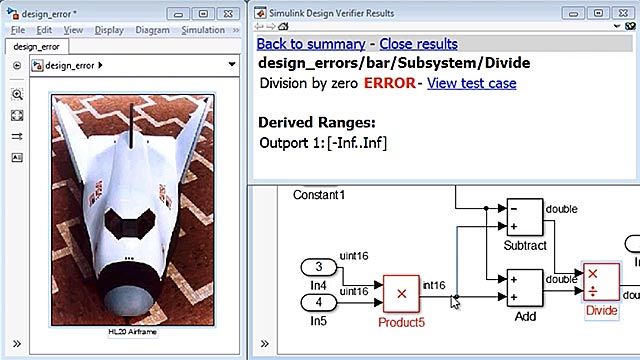

Detección de errores en tiempo de ejecución y errores de diagnóstico

Antes de ejecutar las simulaciones, puede detectar errores en tiempo de ejecución y de modelado, incluidos errores de desbordamiento de enteros, división por cero, array fuera de límites, valores por debajo de lo normal y punto flotante, así como errores de validez de datos.

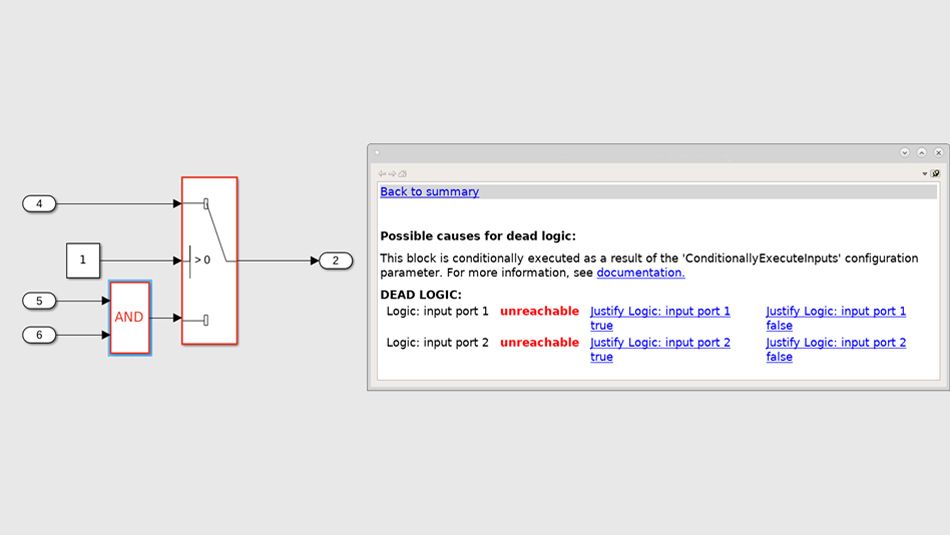

Detección de lógica fallida

Identifique objetos en su modelo que no puedan ser activados durante la simulación y ejecución de código generado.

Análisis de cobertura de pruebas incompleta

Aumente y amplíe casos de prueba existentes creados manualmente para solucionar la cobertura de modelos incompleta, y la cobertura del código generado y el código C/C++, llamado desde bloques de Simulink y diagramas de Stateflow.

Verificación de requisitos de seguridad formales

Verifique si el diseño es conforme con los requisitos de seguridad definidos formalmente (3:53) con MATLAB, Simulink y Stateflow.

Creación de casos de prueba basados en requisitos

Genere casos de prueba a partir de modelos de requisitos del sistema.

Recursos del producto:

“El diseño basado en modelos nos permitió analizar requisitos rápidamente, reutilizar diseños de productos anteriores y eliminar errores de codificación manual, así como reducir los tiempos de desarrollo y acortar los plazos para satisfacer las necesidades de nuestros clientes”.

MyoungSuk Ko, LS Automotive