Deep Learning Processor IP Core Report

When you generate a deep learning processor IP core, Deep Learning HDL Toolbox™ generates an HTML custom IP core report. The report describes the behavior and content of the generated custom IP core. During processor generation, AXI4 slave registers are created to enable MATLAB® or other master devices to control and program the deep learning (DL) processor IP core.

Summary

This section shows the Deep Learning HDL Toolbox settings when you generated the custom IP core.

Target Interface Configuration

This section shows how your model design under test (DUT) ports map to the target hardware interface and the processor/FPGA synchronization mode.

Register Address Mapping

During custom processor generation, AXI4 slave registers are created to enable MATLAB or other master devices to control and program the DL processor IP core.

The DL processor IP core is generated by using the HDL Coder™ IP core generation workflow. The generated IP core contains a standard set of registers. For more information, see Custom IP Core Generation (HDL Coder).

For the full list of register offsets, see the Register Address

Mapping table in the generated deep learning (DL) processor IP core report.

IP Core User Guide

This section gives a high-level overview of the generated IP core architecture and instructions to integrate the IP core into your reference design.

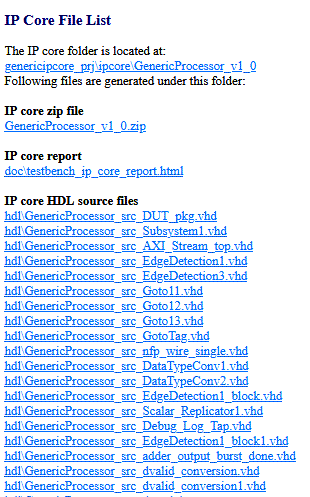

IP Core File List

This section lists the files and folders that are a part of the generated deep learning processor IP core.