Extract Subsystems for Analysis

Overview of Subsystem Extraction

If you have a large model that slows down your analysis or has unreachable objectives, you may want to analyze atomic subsystems or Stateflow® atomic subcharts using Simulink® Design Verifier™. This technique allows you to implement a bottom-up approach to analyzing a large model, as described in Bottom-Up Approach to Model Analysis.

When you analyze a subsystem or atomic subchart, the software:

Extracts the subsystem or subchart into a new model.

If required, adds blocks to the newly created model that replicate the execution context of the subsystem or subchart within its parent model.

Analyzes the extracted model and produces results.

Note

The Simulink Design Verifier software can analyze only atomic subsystems and atomic subcharts. For more information about analyzing subsystems, see Generate Test Cases for a Subsystem. For more information about analyzing atomic subcharts, see Analyze a Stateflow Atomic Subchart.

Simulink Design Verifier does not support extraction of a Variant Subsystem block. For more information on Variant Subsystem block, see Variant Subsystem.

sldvextract Function

The sldvextract function

allows you to extract subsystems and atomic subcharts for component

verification. By extracting the subsystem or atomic subchart, you

can verify the component in isolation from the rest of the system,

allowing you to test the component algorithm. For more information,

see What Is Component Verification? and Functions for Component Verification.

Structure of the Extracted Model

When you analyze a subsystem or atomic subchart, Simulink Design Verifier creates a new model that contains the subsystem or atomic subchart, and any input and output ports that correspond to the ports connected to the original subsystem.

The software assigns the following properties to the ports in the new model, as determined by compiling the original model:

Data types

Sample rates

Signal dimensions

Minimum and maximum values of the signal ranges

The software names the new model subsystem_name,

where subsystem_name is the name of the

subsystem.

The next sections provide examples of how Simulink Design Verifier extracts and analyzes subsystems.

Analyze Simulink Function Subsystems

A data store is a repository to which you can write data, and from which you can read data, without having to connect an input or output signal directly to the data store.

You create a data store using a Data Store Memory block or a Simulink.Signal object. The Data Store Memory block or Simulink.Signal object represents the data store and specifies its properties. Every data store must have a unique name.

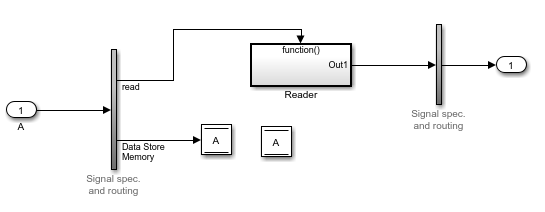

When you analyze a subsystem that reads data from a data store that is accessed outside the subsystem, the analysis:

Adds a Data Store Memory block to the new model.

Adds an input port that writes to the data store. Since the input writes to the data store, the data can have any values (within the specified data type) for the purpose of the Simulink® Design Verifier™ analysis.

If the data store specifies minimum and maximum values, those values are assigned to the new input port.

This example analyzes a subsystem in the sl_subsys_fcncall8 example model.

1. Open the sl_subsys_fcncall8 example model.

open_system('sl_subsys_fcncall8');This model defines a data store A, from which the atomic subsystem Reader reads data using a Data Store Read block.

2. Right-click the Reader subsystem. To add the Design Verifier app options to the menu, point to Select Apps and click the Design Verifier button ![]() . Then, in the Design Verifier app section, select Generate Tests for Subsystem click the Generate Tests button

. Then, in the Design Verifier app section, select Generate Tests for Subsystem click the Generate Tests button ![]() .

.

The Simulink Design Verifier log window shows that the software extracts the subsystem into a new model named Reader, analyzes the extracted model, and offers you the choice of which results to produce.

3. Open the new Reader model that the software created in current_folder\sldv_output\Reader.

The new Inport block A writes into the data store, which is used by the subsystem Reader in the new model.

Analyze Function-Call Subsystems

A function-call subsystem is a triggered subsystem whose execution is determined by logic internal to a C MEX S-function instead of by the value of a signal. Function-call subsystems are always atomic.

For more information, see Implement Function-Call Subsystems with S-Functions.

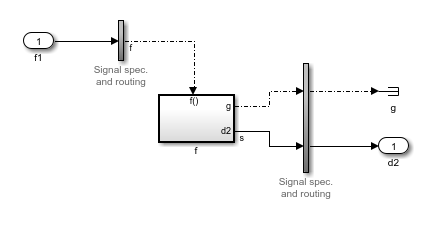

When you analyze a model with a function-call subsystem, Simulink® Design Verifier™ creates a new model with an Inport block that mimics the trigger and a copy of the subsystem. The software then analyzes the new model.

This example analyzes a function-call subsystem in the sl_subsys_fcncall2 model.

1. Open the sl_subsys_fcncall2 example model.

open_system('sl_subsys_fcncall2');2. This model contains a Stateflow® chart named Chart that triggers the function-call subsystem f.

Right-click the f subsystem. To add the Design Verifier app options to the menu, point to Select Apps and click the Design Verifier button ![]() . Then, in the Design Verifier app section, select the Generate Tests for Subsystem click Generate Tests button

. Then, in the Design Verifier app section, select the Generate Tests for Subsystem click Generate Tests button ![]() .

.

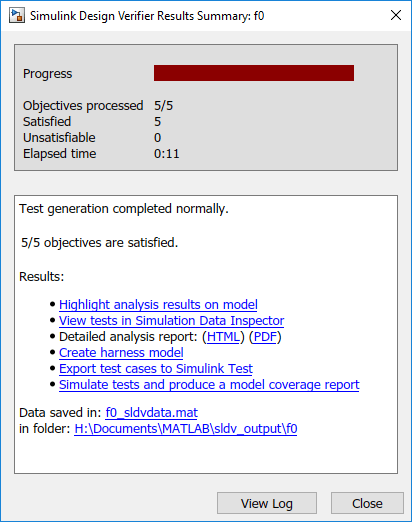

The software extracts the subsystem into a new model named f0, analyzes the extracted model, and produces results.

3. Open the f0 model that the software created in current_folder\sldv_output\f0.

The Inport block and the new subsystem block mimic the trigger for the function-call subsystem f in the new f0 model.

Analyze Global Simulink Function

A Simulink® function is a computational unit that calculates a set of outputs when provided with a set of inputs.

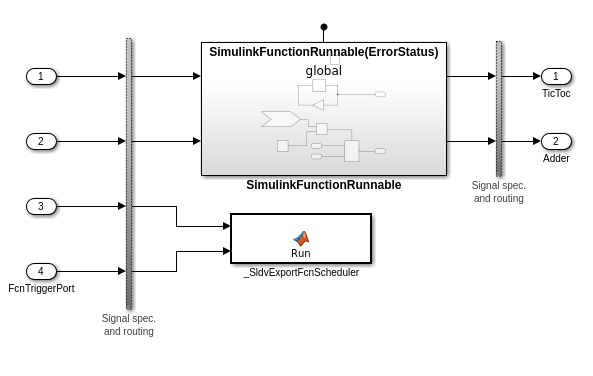

When you analyze Simulink Function subsystem, Simulink Design Verifier™ creates a new model containing a MATLAB® function block _SldvExportFcnScheduler and a copy of the subsystem. This MATLAB Function block invokes Simulink Functions aperiodically and is driven by inports which represent the input arguments of the Simulink Function. An additional Inport block called FcnTriggerPort, the value of which indicates whether to invoke a particular function in a time step or not.

The following example analyzes a global Simulink function in the sldvexGlobalSimFcn model.

1. Open the sldvexGlobalSimFcn model.

open_system('sldvexGlobalSimFcn');2. Right-click the subsystem and in the Design Verifier app section ![]() , click the Generate Tests for Subsystem button

, click the Generate Tests for Subsystem button ![]() .

.

The software extracts the subsystem into a new model and analyzes the extracted model, and produces results.

3. Open the new model SimulinkFunctionRunnable0 that the software creates in current_folder\sldv_output\.

The Inport block FcnTriggerPort, invokes the Simulink Function SimulinkFunctionRunnable in the new SimulinkFunctionRunnable0 model.