Generate Custom Generic Deep Learning Processor IP Core

This example shows how to generate a custom generic deep learning processor IP core. Integrate the generated generic deep learning processor IP core into your larger reference design. To learn how to integrate the generic deep learning processor IP core into your reference design, see Authoring a Reference Design for Live Camera Integration with Deep Learning Processor IP Core.

Create Generic Deep Learning Processor Configuration

Create a custom deep learning processor configuration, by using the dlhdl.ProcessorConfig object. Set the TargetPlatform of the deep learning processor configuration to 'Generic Deep Learning Processor'.

hPC = dlhdl.ProcessorConfig;

hPC.TargetPlatform = 'Generic Deep Learning Processor';Display the modified deep learning processor configuration.

hPC

hPC =

Processing Module "conv"

ModuleGeneration: 'on'

LRNBlockGeneration: 'off'

SegmentationBlockGeneration: 'on'

ConvThreadNumber: 16

InputMemorySize: [227 227 3]

OutputMemorySize: [227 227 3]

FeatureSizeLimit: 2048

Processing Module "fc"

ModuleGeneration: 'on'

SoftmaxBlockGeneration: 'off'

SigmoidBlockGeneration: 'off'

FCThreadNumber: 4

InputMemorySize: 25088

OutputMemorySize: 4096

Processing Module "custom"

ModuleGeneration: 'on'

Addition: 'on'

Multiplication: 'on'

Resize2D: 'off'

Sigmoid: 'off'

TanhLayer: 'off'

InputMemorySize: 40

OutputMemorySize: 40

Processor Top Level Properties

RunTimeControl: 'register'

RunTimeStatus: 'register'

InputStreamControl: 'register'

OutputStreamControl: 'register'

SetupControl: 'register'

ProcessorDataType: 'single'

System Level Properties

TargetPlatform: 'Generic Deep Learning Processor'

TargetFrequency: 200

SynthesisTool: 'Xilinx Vivado'

ReferenceDesign: ''

SynthesisToolChipFamily: 'Zynq UltraScale+'

SynthesisToolDeviceName: 'xczu9eg-ffvb1156-2-e'

SynthesisToolPackageName: ''

SynthesisToolSpeedValue: ''

The generic deep learning processor configuration generates a generic Xilinx® IP core. To generate a generic Intel® core, enter:

hPC.SynthesisTool = 'Altera QUARTUS II'

Generate Generic Deep Learning Processor IP Core

Generate a generic deep learning processor IP core by using the dlhdl.buildProcessor function. Set the ProjectFolder, ProcessorName, and TargetLanguage properties of the generic deep learning processor.

dlhdl.buildProcessor(hPC,'ProjectFolder','genericipcore_prj','ProcessorName','GenericProcessor','HDLCoderConfig',{'TargetLanguage','VHDL'})

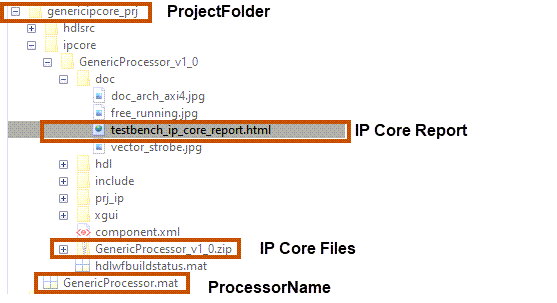

This image shows the files generated for the generic deep learning processor IP core.

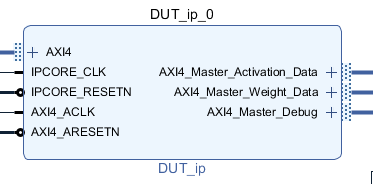

This image shows the generated generic deep learning processor IP core:

The generic IP core consists of:

An AXI4 slave interface called

AXI4.Three AXI4 master interfaces for activation, weights, and utility or debug data.

The dlhdl.buildProcessor function also generates an IP core generation report that contains:

Register address mapping table

IP core user guide

IP core file list

For more information, see Deep Learning Processor IP Core Report.

See Also

dlhdl.ProcessorConfig | dlhdl.buildProcessor