FFT

Compute fast Fourier transform (FFT)

Libraries:

DSP HDL Toolbox /

Transforms

Description

The FFT block provides two architectures that implement the algorithm for FPGA and ASIC applications. You can select an architecture that optimizes for either throughput or area.

Streaming Radix 2^2— Use this architecture for high-throughput applications. This architecture supports scalar or vector input data. You can achieve gigasamples-per-second (GSPS) throughput, also called super sample rates, using vector input. Since 2025a, this architecture also supports specifying the FFT size by using an input port, when you use scalar input data.Burst Radix 2— Use this architecture for a minimum resource implementation, especially with large fast-Fourier-transform (FFT) sizes. Your system must be able to tolerate bursty data and higher latency. This architecture supports only scalar input data.

The block accepts real or complex data, provides hardware-friendly control signals, and optional output frame control signals.

Note

You can also generate HDL code for this hardware-optimized algorithm, without creating a Simulink® model, by using the DSP HDL IP Designer app. The app provides the same interface and configuration options as the Simulink block.

Examples

Implement an inverse fast Fourier transform (IFFT) by using a forward FFT block.

Instead of deploying a dedicated IFFT block, this design reuses an FFT block to calculate the inverse FFT by swapping the real and imaginary parts of the data both before and after the FFT operation. With this implementation, you can reuse a single FFT block to perform both FFT and IFFT computations in hardware, as long as you do not require both operations at the same time. This approach is well suited for FPGA or ASIC designs that have limited hardware resources.

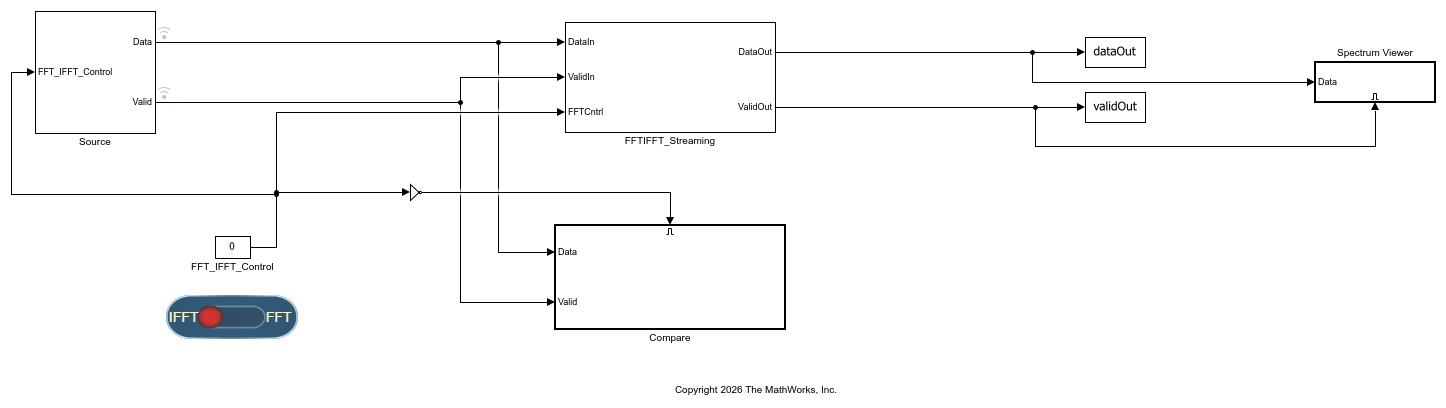

Model Overview

The top-level model includes these features:

Input Signal Generation

IFFT Implementation Using FFT with Real/Imaginary Swapping

Result Visualization

The model operates on complex data and uses a streaming interface with control signals to indicate when the data is valid. The system processes 8 samples per cycle and implements a 512-point FFT/IFFT.

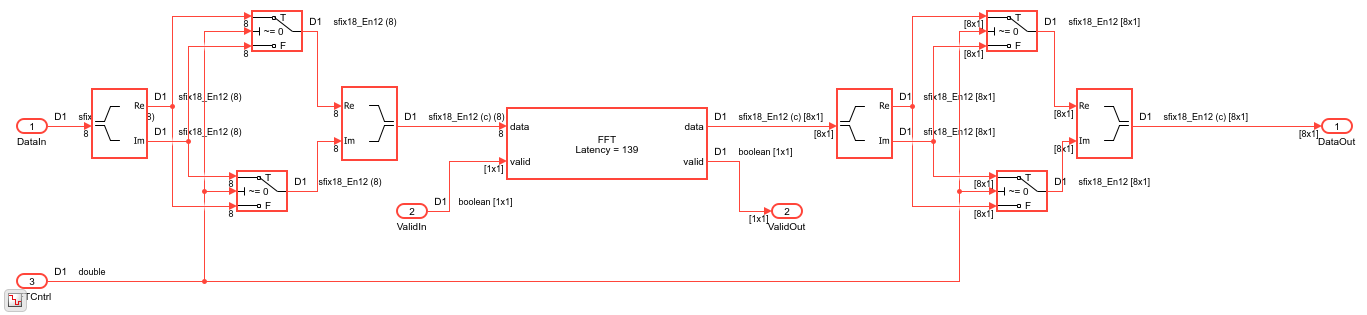

The FFTIFFT_Streaming subsystem contains the FFT block from the DSP HDL Toolbox™ library and swapping logic.

Use the toggle switch to select between FFT and IFFT modes. Set FFT_IFFT_Control signal to 0 for IFFT mode or to 1 for FFT mode. The switch enables or disables the swapping logic inside the FFTIFFT_Streaming subsystem and modifies the source output.

The Spectrum Viewer subsystem reorders the output samples to account for the bit-reversed order from the FFT block, and plots the output. The model also exports output data to the workspace.

modelname = 'FFTIFFTHDL_Streaming'; open_system(modelname); % Set scope time interval. scopePath = [modelname '/Spectrum Viewer/Time Scope']; set_param(scopePath, 'TimeSpan', num2str(20));

Generate Input Signal

The source subsystem generates frames of 512 complex input samples in the time-domain. In IFFT mode, the source returns the FFT of the time-domain signal. The MATLAB® code generates the signal, casts it to a fixed-point type, and generates a corresponding valid signal. The valid signal indicates when each input sample is available for processing, ensuring synchronization with the FFT block.

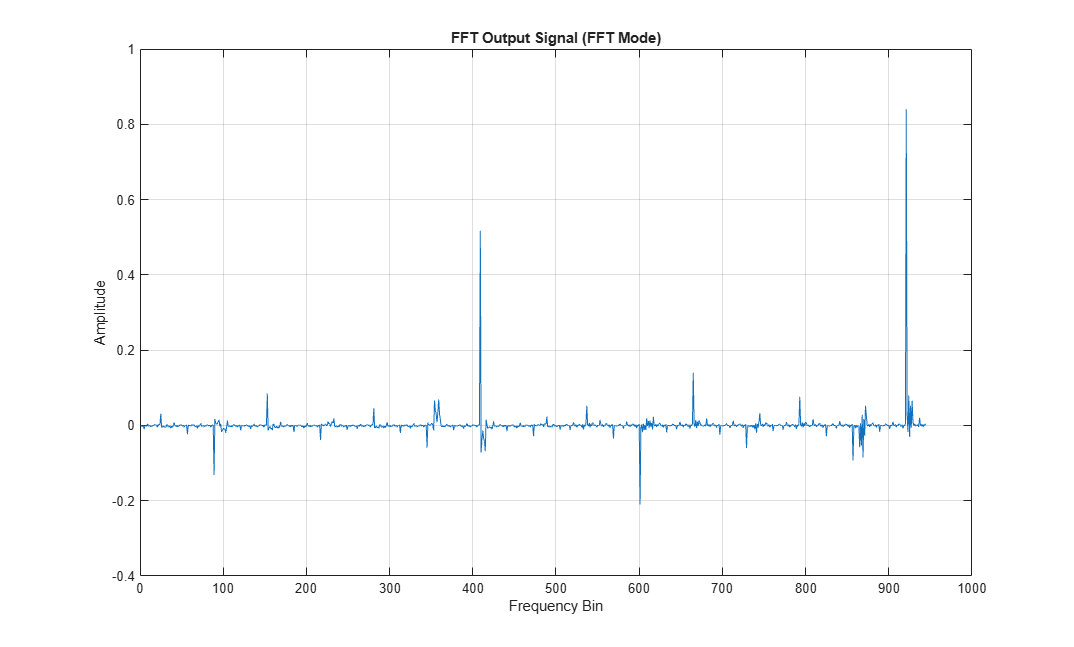

FFT Operation

When you set the FFT_IFFT_Control signal to 1 (FFT mode), the model computes the 512-point FFT of the input frame and outputs the frequency-domain representation of the signal.

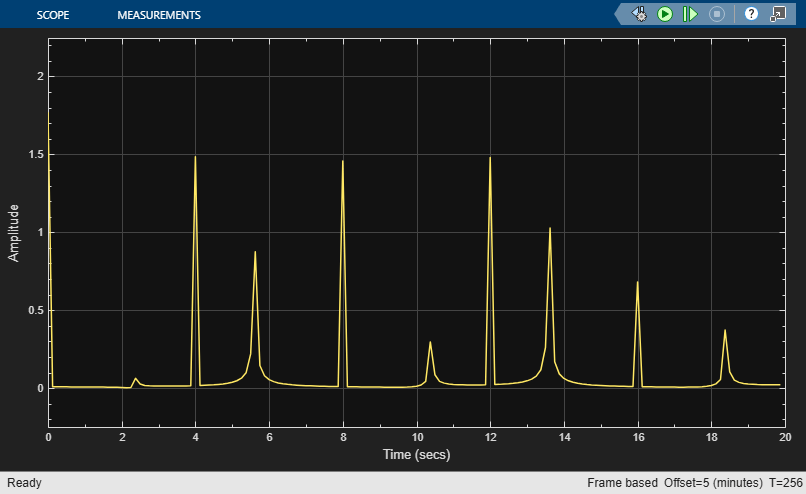

Set FFT_IFFT_Control to FFT mode and run the model to capture the FFT output. The plot shows the real part of the FFT output for the current frame. You can use this output to analyze the frequency content of the input signal.

set_param([modelname '/FFT_IFFT_Control'], 'Value', '1'); sim(modelname);

Visualize the FFT output.

FFTOutput = squeeze(dataOut(:,:,validOut)); figure; plot(real(FFTOutput(:))); xlabel('Frequency Bin'); ylabel('Amplitude'); title('FFT Output Signal (FFT Mode)'); grid on;

Inverse FFT Algorithm

The FFTIFFT_Streaming subsystem computes the IFFT by using a forward FFT block and swapping the real and imaginary parts.

Input Swapping: The model separates the complex input signal into real and imaginary components, then swaps and recombines the components to create a new complex data signal. The valid signal remains aligned with the swapped data.

FFT Processing: The model passes the swapped complex signal to a forward FFT block configured for a length of 512 samples. The FFT block produces output in bit-reversed order.

Output Swapping: The model splits the FFT output into real and imaginary parts, then swaps and recombines the components a second time.

Mathematically, this process is:

![$$x'[n] = \mathrm{Im}(x[n]) + j\,\mathrm{Re}(x[n])$$](../../examples/dsphdl/win64/CalculateInverseFFTUsingAForwardFFTBlockHDLExample_eq05484494437333196802.png)

![$$X'[k] = \mathrm{FFT}(x'[n])$$](../../examples/dsphdl/win64/CalculateInverseFFTUsingAForwardFFTBlockHDLExample_eq10114284411887094959.png)

![$$y[k] = \mathrm{Im}(X'[k]) + j\,\mathrm{Re}(X'[k])$$](../../examples/dsphdl/win64/CalculateInverseFFTUsingAForwardFFTBlockHDLExample_eq07043485408952949663.png)

Now, set FFT_IFFT_Control to IFFT mode and run the model.

open_system([modelname '/FFTIFFT_Streaming']); set_param([modelname '/FFT_IFFT_Control'],'Value','0'); sim(modelname);

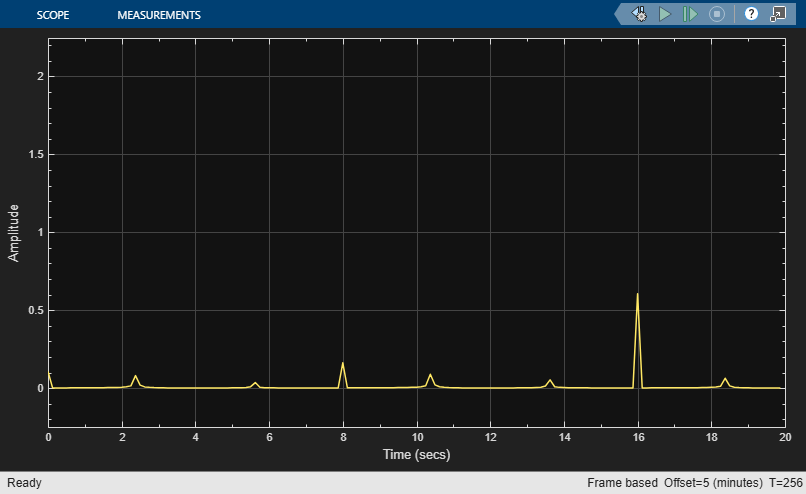

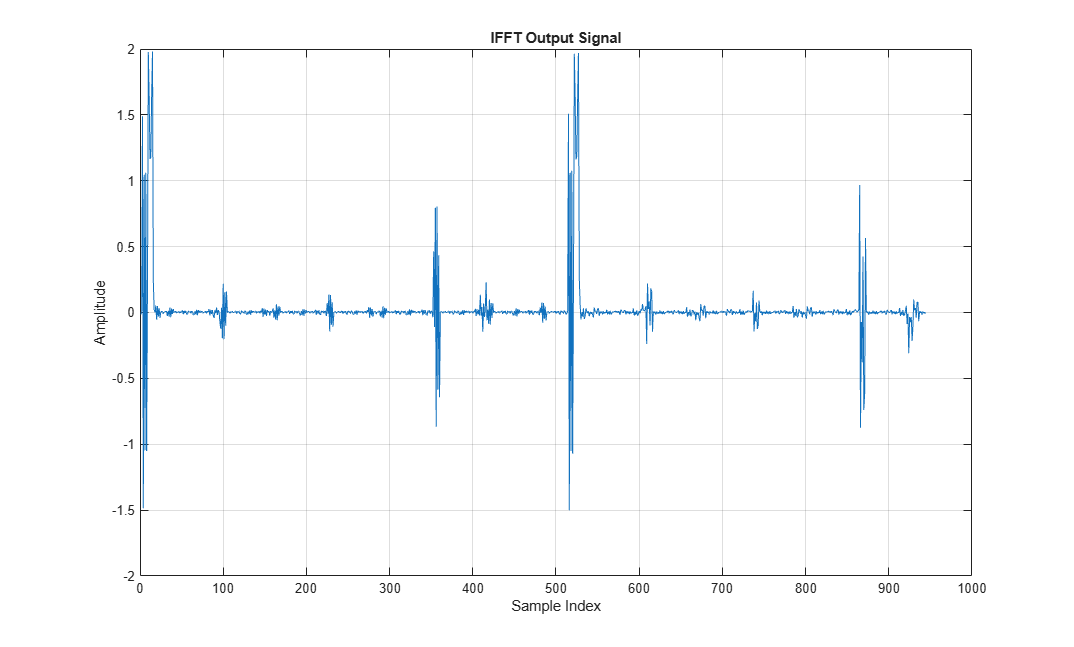

Visualize IFFT Result

The figure shows the time-domain signal reconstructed by the IFFT operation. The x-axis shows the sample index, and the y-axis shows the amplitude of each sample. Each stem corresponds to a time-domain sample obtained after calculating the IFFT of the frequency-domain signal with swapped real and imaginary parts.

IFFTOutput = squeeze(dataOut(:,:,validOut)); figure; plot(real(IFFTOutput(:))); xlabel('Sample Index'); ylabel('Amplitude'); title('IFFT Output Signal'); grid on;

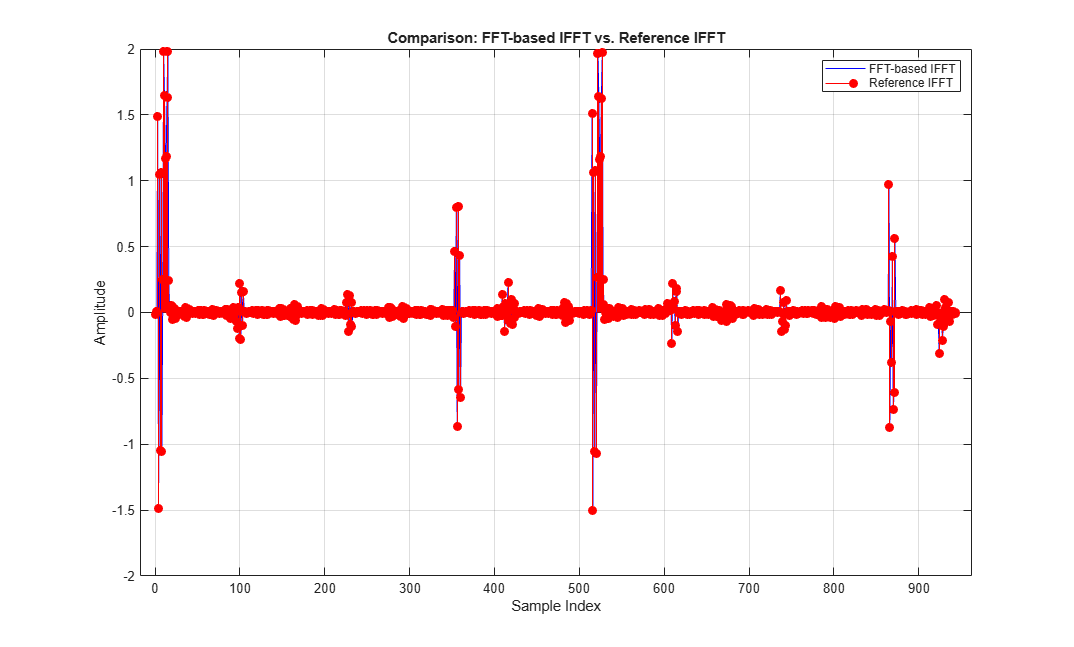

Compare with Reference IFFT

To verify the implementation, compare the output of the FFT-based IFFT method with a standard IFFT block from DSP HDL Toolbox™. The plots show both outputs for comparison.

validDataRef = squeeze(refOut(:,:,refValidOut)); figure; plot(real(IFFTOutput(:)),'b'); % Blue line for IFFTOutput hold on; stem(real(validDataRef(:)),'r','filled','Marker','o'); xlabel('Sample Index'); ylabel('Amplitude'); title('Comparison: FFT-based IFFT vs. Reference IFFT'); legend('FFT-based IFFT','Reference IFFT'); grid on; hold off;

The output matches the result of a dedicated IFFT implementation. This technique enables efficient resource sharing and suits FPGA and ASIC designs where minimizing logic usage is important.

More Design Options

An alternative way to implement the IFFT using an FFT block is the conjugate method. You can perform the IFFT by finding the complex conjugate of the input signal, then running it through the FFT block, finding the complex conjugate of the FFT output, and finally dividing the result by the FFT length (N). The method shown in this example is a slightly simpler algorithm with less logic.

Extended Examples

Implement FFT Algorithm for FPGA

Implement two hardware-optimized FFT architectures in Simulink.

Frequency-Domain Filtering in HDL

Implement a filter in the frequency domain. The filter is built with the FFT and IFFT blocks from DSP HDL Toolbox™.

Automatic Delay Matching for the Latency of FFT Block

Programmatically obtain the latency of an FFT block in a model for use in delay matching.

Ports

Input

Input data, specified as a scalar or column vector of real or complex values.

Vector input is supported with the Streaming Radix 2^2

architecture, and not supported with variable FFT size. The vector size must be a

power of 2, in the range from 1 to 64, and less than or equal to the FFT

length.

The software supports double and

single data types for simulation, but not for HDL code generation.

Data Types: fixed point | int8 | int16 | int32 | int64 | uint8 | uint16 | uint32 | uint64 | single | double

Complex Number Support: Yes

Control signal that indicates if the input data is valid. When

valid is 1 (true), the

block captures the values from the input data port. When

valid is 0 (false), the

block ignores the values from the input data port.

When you set the Architecture parameter to Burst

Radix 2, or set the FFT length source parameter

to Input port, you must respect the

ready backpressure signal.

Data Types: Boolean

Since R2025a

Provide the FFT size as

log2(FFTLength). For

example, if the FFT length is 32, specify 5 at the port. For HDL

code generation, the FFT length must be a power of 2 between

22 and 216, so the port value

must be in the range 2 to 16. If the value is less than 2, the block uses an FFT

length of 4. If the value is greater than 16, the block uses an FFT length of

216. If you set log2FFTLen to a size

larger than the Maximum FFT length parameter value, the block

performs the FFT calculations using the Maximum FFT length

parameter value.

To notify the block of the new FFT length, set loadFFTLen to

1 (true) for at least one cycle with a new

value on log2FFTLen.

Variable-size FFT designs must respect the ready backpressure

signal. When you load a new FFT length, the block sets ready to

0 (false) while it updates internal logic with

the new size. If the block is processing a previous frame when you load a new FFT

size, the block finishes the frame and then updates internal logic to use the new

size. For more information, see the Control Signals

section.

Dependencies

To enable this port, set the FFT length source parameter to

Input port.

Data Types: fixdt(0,M,0) where 1<M<6

Since R2025a

Control signal that indicates if the input FFT size is valid. When

loadFFTLen is 1 (true),

the block captures the value from the input log2FFTLen port. When

loadFFTLen is 0 (false),

the block ignores the value from the input log2FFTLen

port.

Dependencies

To enable this port, set the FFT length source parameter to

Input port.

Data Types: Boolean

Control signal that clears internal states. When reset is

1 (true), the block stops the current

calculation and clears internal states. When the reset is

0 (false) and the input

valid is 1 (true), the

block captures data for processing.

For more reset considerations, see the Reset Signal section on the Hardware Control Signals page.

Dependencies

To enable this port, on the Control Ports tab, select the Enable reset input port parameter.

Data Types: Boolean

Output

Output data, returned as a scalar or column vector of complex values. When input is fixed-point data type and scaling is enabled, the output data type is the same as the input data type. When the input is integer type and scaling is enabled, the output is fixed-point type with the same word length as the input integer. The output order is bit-reversed by default. If scaling is disabled, the output word length increases to avoid overflow. For more information on FFT scaling, see the Divide butterfly outputs by two parameter.

Data Types: fixed point | double | single

Complex Number Support: Yes

Control signal that indicates if the output data is valid. When

valid is 1 (true), the

block returns valid data from the output data port. When

valid is 0 (false), the

values from the output data port are not valid.

Data Types: Boolean

Control signal that indicates the block can accept new input data. The block sets

this output to 1 (true) when it can accept data,

and to 0 (false) when it is processing and

cannot accept more data.

The ready signal operates differently depending on whether you use the burst algorithm or the variable-size FFT. For details, see the Control Signals section.

Dependencies

To enable this port, set the Architecture parameter to

Burst Radix 2, or with

Architecture set to Streaming Radix

2^2, set the FFT length source parameter to

Input port.

Data Types: Boolean

Control signal that indicates the first valid cycle of the output frame. When

start is 1 (true), the

block returns the first valid sample of the frame on the output

data port.

Dependencies

To enable this port, on the Control Ports tab, select the Enable start output port parameter.

Data Types: Boolean

Control signal that indicates the last valid cycle of the output frame. When

end is 1 (true), the

block returns the last valid sample of the frame on the output

data port.

Dependencies

To enable this port, on the Control Ports tab, select the Enable end output port parameter.

Data Types: Boolean

Parameters

Note

These parameters apply when configuring a block in Simulink or an algorithm in the DSP HDL IP Designer app.

Main

Specify the hardware implementation for the FFT.

Streaming Radix 2^2— Low-latency architecture. This architecture supports GSPS throughput when you use vector input. Since R2025a, this architecture supports variable FFT length. When you use variable FFT length, your input data must comply with the ready backpressure signal.Burst Radix 2— Minimum resource architecture. This architecture does not support vector input. When you use this architecture, your input data must comply with the ready backpressure signal. This architecture supports only fixed FFT lengths.

For more details about these architectures, see Algorithms.

Since R2025a

You can enter a constant FFT length as a parameter or provide time-varying FFT

length by using an input port. When you select Input port,

the log2FFTLen, loadFFTLen, and

ready ports appear on the block.

Dependencies

This parameter is only available when you set Architecture

to Streaming Radix 2^2.

When you select Input port, the Output in

bit-reversed order and Input in bit-reversed order

parameters are disabled. The block uses natural input order and bit-reversed output

order.

Specify the number of data points used for one FFT calculation. For HDL code generation, the FFT length must be a power of 2 between 22 and 216.

Dependencies

This parameter is available when you set Architecture to

Burst Radix 2 or you set the FFT length

source parameter to Property.

Since R2025a

Specify the maximum number of data points used for one FFT calculation. This parameter can help limit the hardware resources needed for a variable-size FFT design. The Maximum FFT length must be a power of 2 between 23 to 216.

If you provide an input frame after reset without setting the FFT length from the port, the block uses the Maximum FFT length parameter value.

If you set log2FFTLen to a size larger than the Maximum FFT length parameter value, the block performs the FFT calculations using the Maximum FFT length parameter value.

Dependencies

This parameter is available when you set the FFT length

source parameter to Input port.

Specify the hardware implementation for complex multipliers. Each multiplication

is implemented either with Use 4 multipliers and 2 adders

or with Use 3 multipliers and 5 adders. Depending on your

synthesis tool and target device, one option may be faster or smaller.

When you select this check box, the output elements are bit-reversed relative to the input order. To return output elements in linear order, clear this check box.

The FFT algorithm calculates output in the reverse order to the input. If you specify the output to be in the same order as the input, the algorithm performs an extra reversal operation. For more information, see Linear and Bit-Reversed Output Order.

Dependencies

When you set the FFT length source parameter to

Input port, the Output in bit-reversed

order and Input in bit-reversed order parameters

are disabled. The block uses natural input order and bit-reversed output order.

When you select this check box, the block expects input data in bit-reversed order. By default, the check box is cleared and the input is expected in linear order.

The FFT algorithm calculates output in the reverse order to the input. If you specify the output to be in the same order as the input, the algorithm performs an extra reversal operation. For more information, see Linear and Bit-Reversed Output Order.

Dependencies

When you set the FFT length source parameter to

Input port, the Output in bit-reversed

order and Input in bit-reversed order parameters

are disabled. The block uses natural input order and bit-reversed output order.

When you select this parameter, the FFT implements an overall 1/FFTLength scale factor by dividing the output of each butterfly multiplication by two. This adjustment keeps the output of the FFT in the same amplitude range as its input. If you disable scaling, the FFT avoids overflow by increasing the word length by 1 bit after each butterfly multiplication. The bit growth is the same for both architectures.

Data Types

Rounding mode used for internal fixed-point calculations. When the input is any

integer or fixed-point data type, this block uses fixed-point arithmetic for internal

calculations. This option does not apply when the input data is

single or double type. Rounding applies to

twiddle-factor multiplication and scaling operations. For more information about

rounding modes, see Rounding Modes.

Control Ports

Enable the input reset port on the block.

Enable the output start port on the block. This output signal indicates the first sample of a frame of output data.

Enable the output end port on the block. This output signal indicates the last sample of a frame of output data.

Algorithms

The streaming Radix 2^2 architecture implements a low-latency architecture. It saves resources compared to a streaming Radix 2 implementation by factoring and grouping the FFT equation. The architecture has log4(N) stages. Each stage contains two single-path delay feedback (SDF) butterflies with memory controllers. When you use vector input, each stage operates on fewer input samples, so some stages reduce to a simple butterfly, without SDF.

The first SDF stage is a regular butterfly. The second stage multiplies the outputs of the first stage by –j. To avoid a hardware multiplier, the block swaps the real and imaginary parts of the inputs, and again swaps the imaginary parts of the resulting outputs. Each stage rounds the result of the twiddle factor multiplication to the input word length. The twiddle factors have two integer bits, and the rest of the bits are used for fractional bits. The twiddle factors have the same bit width as the input data, WL. The twiddle factors have two integer bits, and WL-2 fractional bits.

If you enable scaling, the algorithm divides the result of each butterfly stage by 2. Scaling at each stage avoids overflow, keeps the word length the same as the input, and results in an overall scale factor of 1/N. If scaling is disabled, the algorithm avoids overflow by increasing the word length by 1 bit at each stage. The diagram shows the butterflies and internal word lengths of each stage, not including the memory.

The burst Radix 2 architecture implements the FFT by using a single complex butterfly multiplier. The algorithm cannot start until it has stored the entire input frame, and it cannot accept the next frame until computations are complete. The output ready port indicates when the algorithm is ready for new data. The diagram shows the burst architecture, with pipeline registers.

When you use this architecture, your input data must comply with the ready backpressure signal.

The algorithm processes input data only when the input valid port is 1. Output data is valid only when the output valid port is 1.

When the optional input reset port is 1, the algorithm stops the current calculation and clears all internal states. The algorithm begins new calculations when reset port is 0 and the input valid port starts a new frame.

This diagram shows the input and output valid input values for contiguous scalar input data, streaming Radix 2^2 architecture, an FFT length of 1024, and a vector size of 16.

The diagram also shows the optional start and end outputs that indicate frame boundaries. If you enable the start output, the start output pulses for one cycle with the first valid output of the frame. If you enable the end output, the end output pulses for one cycle with the last valid output of the frame.

If you apply continuous input frames, the output will also be continuous after the initial latency.

The valid input can be noncontiguous. The algorithm processes data accompanied by a validsignal as it arrives, and stores the resulting data until a frame is filled. Then the algorithm returns contiguous output samples in a frame of N (FFT length) cycles. This diagram shows noncontiguous input and contiguous output for an FFT length of 512 and a vector size of 16.

When you use the burst architecture, you cannot provide the next frame of input data until

memory space is available. The ready output indicates when the

algorithm can accept new input data. The algorithm sets the ready

output to 1 (true) when it can accept data, and to

0 (false) when it is processing and cannot accept

more data. If the upstream part of your design has continuous input data and synchronously

reacts to ready before halting input, then one extra cycle of input

data can arrive at the port. This data is the beginning of the next frame. To support

synchronous control logic, the block reserves room to store this extra data while processing

the current frame. For more detail about this extra data, see the annotated waveform in the

Latency

section.

Variable-size FFT designs must also respect the ready signal. When

you load a new FFT length, the algorithm sets ready to

0 (false) while it updates internal logic with the

new size. If the algorithm is processing a previous frame when you load a new FFT size, the

algorithm finishes the frame and then updates internal logic to use the new size.

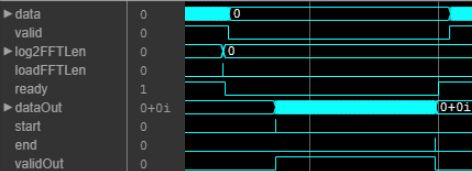

The first waveform shows loading the input size before any frame is processed. The

algorithm sets the ready signal to 0

(false) for 4 cycles while it updates internal logic with the new

size, and then sets ready to 1

(true) again. The waveform shows new input data and

valid set to 1 (true) once

the ready signal is 1 (true)

again.

The next waveform shows loading a new FFT size while a frame is processing. When you load

a new size, the algorithm sets the ready signal to 0

(false). You can continue to provide the rest of the current input

frame. The block sets ready to 1

(true) when it has completed the current frame and updated the

internal logic with the new size. You can apply the next frame, of the new size, once the

ready signal is 1 (true).

The latency varies with the FFT length and input vector size. After you update the model, the block icon displays the latency. The displayed latency is the number of cycles between the first valid input and the first valid output, assuming the input is contiguous. To obtain this latency programmatically, see Automatic Delay Matching for the Latency of FFT Block.

When using the burst

architecture, if the upstream part of your design has continuous input data and synchronously

reacts to ready before halting input, then one extra cycle of input data

can arrive at the port. This data is the beginning of the next frame. To support synchronous

control logic, the block reserves room to store this extra data while processing the current

frame. Due to this one cycle advance, the observed latency of the later frames (cycles from

first input valid to first output valid) is one cycle

shorter than the reported latency. The number of cycles between when ready

port is 0 (false) and the output

valid port is 1 (true) is always

latency – FFTLength.

This resource and performance data is the synthesis result from the generated HDL targeted to a Xilinx® Virtex®-6 (XC6VLX75T-1FF484) FPGA. The examples in the tables have this configuration:

1024 FFT length (default)

Complex multiplication using 4 multipliers, 2 adders

FFT scaling enabled

Natural order input, Bit-reversed output

16-bit complex input data

Clock enables minimized (HDL Coder™ parameter)

Performance of the synthesized HDL code varies with your target and synthesis options. For instance, reordering for a natural-order output uses more RAM than the default bit-reversed output, and real input uses less RAM than complex input.

For a scalar input Radix 2^2 configuration, the design achieves 326 MHz clock frequency. The latency is 1116 cycles. The design uses these resources.

| Resource | Number Used |

|---|---|

| LUT | 4597 |

| FFS | 5353 |

Xilinx LogiCORE® DSP48 | 12 |

| Block RAM (16K) | 6 |

When you vectorize the same Radix 2^2 implementation to process two 16-bit input samples in parallel, the design achieves 316 MHz clock frequency. The latency is 600 cycles. The design uses these resources.

| Resource | Number Used |

|---|---|

| LUT | 7653 |

| FFS | 9322 |

Xilinx LogiCORE DSP48 | 24 |

| Block RAM (16K) | 8 |

When using the burst Radix 2 architecture, the block supports only scalar input data. The burst design achieves 309 MHz clock frequency. The latency is 5811 cycles. The design uses these resources.

| Resource | Number Used |

|---|---|

| LUT | 971 |

| FFS | 1254 |

Xilinx LogiCORE DSP48 | 3 |

| Block RAM (16K) | 6 |

When you specify FFT length from the input port, the block implements an internal FFT

using the Maximum FFT length value. There is also a small amount of

logic to store and load the FFT length from the port, and one extra multiplier stage. When

you specify FFT length from a port, the block supports only scalar input data. The design

achieves 375 MHz clock frequency. The latency changes with the FFT length. With the

Maximum FFT length parameter set to 1024, the

design uses these resources.

| Resource | Number Used |

|---|---|

| LUT | 7991 |

| FFS | 7902 |

Xilinx LogiCORE DSP48 | 20 |

| Block RAM (16K) | 4 |

References

[1] Algnabi, Y.S, F.A. Aldaamee, R. Teymourzadeh, M. Othman, and M.S. Islam. “Novel architecture of pipeline Radix 2^2 SDF FFT Based on digit-slicing technique.” 10th IEEE International Conference on Semiconductor Electronics (ICSE). 2012, pp. 470–474.

Extended Capabilities

This block supports C/C++ code generation for Simulink accelerator and rapid accelerator modes and for DPI component generation.

HDL Coder provides additional configuration options that affect HDL implementation and synthesized logic.

This block has one default HDL architecture.

| ConstrainedOutputPipeline | Number of registers to place at

the outputs by moving existing delays within your design. Distributed

pipelining does not redistribute these registers. The default is

|

| InputPipeline | Number of input pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| OutputPipeline | Number of output pipeline stages

to insert in the generated code. Distributed pipelining and constrained

output pipelining can move these registers. The default is

|

| SynthesisAttributes |

Specifies the synthesis attributes for the blocks and block output signals in the model. The generated HDL code contains these attributes. For more information, see SynthesisAttributes (HDL Coder). |

You cannot generate HDL code for this block inside an Enabled Subsystem (Simulink).

Version History

Introduced in R2014aYou can now specify time-varying FFT length by using an input port. This feature is

supported only when you set Architecture to Streaming

Radix 2^2 and you use scalar input data.

Set FFT length source parameter to Input

port, and then specify the FFT length at the log2FFTLen

port as log2(FFTLength). For

example, if the FFT length is 32, specify 5 at the port. Set the

loadFFTLen port to 1 (true) for

at least one cycle to capture the value from the input log2FFTLen

port.

Variable-size FFT designs must respect the ready backpressure

signal. When you load a new FFT length, the block sets ready to

0 (false) while it updates internal logic with the

new size. If the block is processing a previous frame when you load a new FFT size, the

block finishes the frame and then updates internal logic to use the new size. For more

information, see the Control Signals section.

To limit the hardware resources used in the variable-sized FFT implementation, set the Maximum FFT length parameter to your expected maximum input size.

Before R2022a, this block was named FFT HDL Optimized and was included in the DSP System Toolbox™ DSP System Toolbox HDL Support library.

You can now set the FFT length to 4 (22). In previous releases the FFT length had to be a power of 2 from 8 (23) to 216.

MATLAB Command

You clicked a link that corresponds to this MATLAB command:

Run the command by entering it in the MATLAB Command Window. Web browsers do not support MATLAB commands.

Seleccione un país/idioma

Seleccione un país/idioma para obtener contenido traducido, si está disponible, y ver eventos y ofertas de productos y servicios locales. Según su ubicación geográfica, recomendamos que seleccione: .

También puede seleccionar uno de estos países/idiomas:

Cómo obtener el mejor rendimiento

Seleccione China (en idioma chino o inglés) para obtener el mejor rendimiento. Los sitios web de otros países no están optimizados para ser accedidos desde su ubicación geográfica.

América

- América Latina (Español)

- Canada (English)

- United States (English)

Europa

- Belgium (English)

- Denmark (English)

- Deutschland (Deutsch)

- España (Español)

- Finland (English)

- France (Français)

- Ireland (English)

- Italia (Italiano)

- Luxembourg (English)

- Netherlands (English)

- Norway (English)

- Österreich (Deutsch)

- Portugal (English)

- Sweden (English)

- Switzerland

- United Kingdom (English)