Reference Design Integration and Deployment

You can integrate the generated IP core into the default system reference design or into your own custom reference design that you register for the board. HDL Coder™ can generate an IP core, integrate it into your Vivado® project, and program the hardware. Using Embedded Coder®, you can generate and build the embedded software, and run it on the ARM® processor.

Topics

- Default System Reference Design for AMD SoC Device

Learn about the default system reference design for AMD® SoC device and using the reference design.

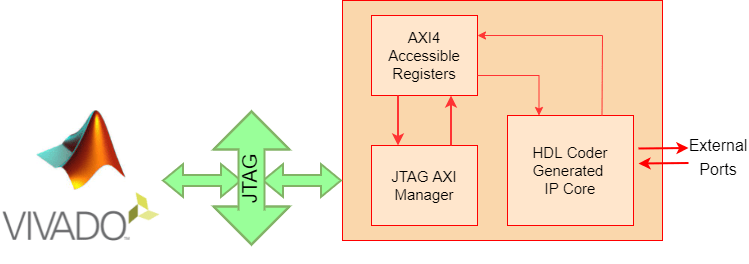

- Default System Reference Design for AMD FPGA Board

Learn about the default system reference design for AMD FPGA board and using the reference design.

- Default System with AXI4-Stream Interface Reference Design

Learn about how to use the default system with AXI4-Stream Interface reference design and its requirements.

- Default Video System Reference Design

Learn about the default video system reference design and its requirements.

- Default System with External DDR Memory Access Reference Design

Learn about the default system with external DDR3, DDR4, and LPDDR4 memory access reference design and its requirements.

- Program Target FPGA Boards or SoC Devices

How to program the target Intel or Xilinx Hardware.