Hold time (ns)

Hold time for input signals and forced reset input signals

Model Configuration Pane: Test Bench

Description

Specify a hold time, in nanoseconds, for input signals and forced reset input signals.

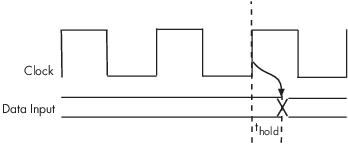

Hold Time for Reset Input Signals

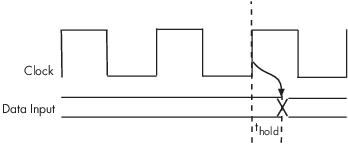

The hold time is the amount of time that reset input signals and input data are held past the clock rising edge. The following figures show the application of a hold time (thold) for reset and data input signals when the signals are forced to active high and active low.

Hold Time for Data Input Signals

Note

A reset signal is always asserted for two cycles plus thold.

Dependencies

This option is disabled if you select the entire model. Select the DUT instead for Generate HDL for setting.

Settings

2 (default)The hold time defines the number of nanoseconds that reset input signals and input data are held past the clock rising edge. The hold time is expressed as a positive integer or double (with a maximum of 6 significant digits after the decimal point).

Tips

The specified hold time must be less than the clock period (specified by the Clock high time and Clock low time properties).

This option applies to reset input signals only if Force reset is selected.

To set this property, use hdlset_param or makehdltb. To view the property value, use hdlget_param.

For example, you can specify this parameter for the symmetric_fir subsystem inside the sfir_fixed model using either of these methods.

Pass the property as an argument to the

makehdltbfunction.makehdltb('sfir_fixed/symmetric_fir', ... 'HoldTime', 4)

When you use

hdlset_param, you can set the parameter on the model and then generate HDL code usingmakehdltb.hdlset_param('sfir_fixed', 'HoldTime', 4) makehdltb('sfir_fixed/symmetric_fir')

Recommended Settings

No recommendations.

Programmatic Use

Parameter: HoldTime |

| Type: integer |

| Value: positive integer |

| Default: 2 |

Version History

Introduced in R2012a