Generate HDL Code from Simulink Model Using Configuration Parameters

You can view and edit options and parameters that affect HDL code generation in the Configuration Parameters dialog box, or in the Model Explorer. This example illustrates how you can use the Configuration Parameters dialog box to generate HDL code for the Symmetric FIR filter model.

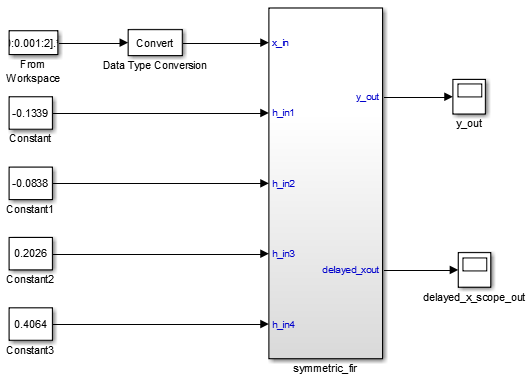

FIR Filter Model

Before you generate HDL code, the model must be compatible for HDL code generation. To check and update your model for HDL compatibility, see Check HDL Compatibility of Simulink Model Using HDL Code Advisor.

This example uses the Symmetric FIR filter model that is compatible for HDL code generation. To open this model at the command line, enter:

sfir_fixed

The model uses a division of labor that is suitable for HDL design.

The

symmetric_firsubsystem, which implements the filter algorithm, is the device under test (DUT). An HDL entity is generated from this subsystem.The top-level model components that drive the subsystem work as a test bench.

The top-level model generates 16-bit fixed-point input signals for

the symmetric_fir subsystem. The Signal From Workspace block

generates a test input (stimulus) signal for the filter. The four

Constant blocks provide filter coefficients. The

Scope blocks are used for simulation and are not used for HDL

code generation.

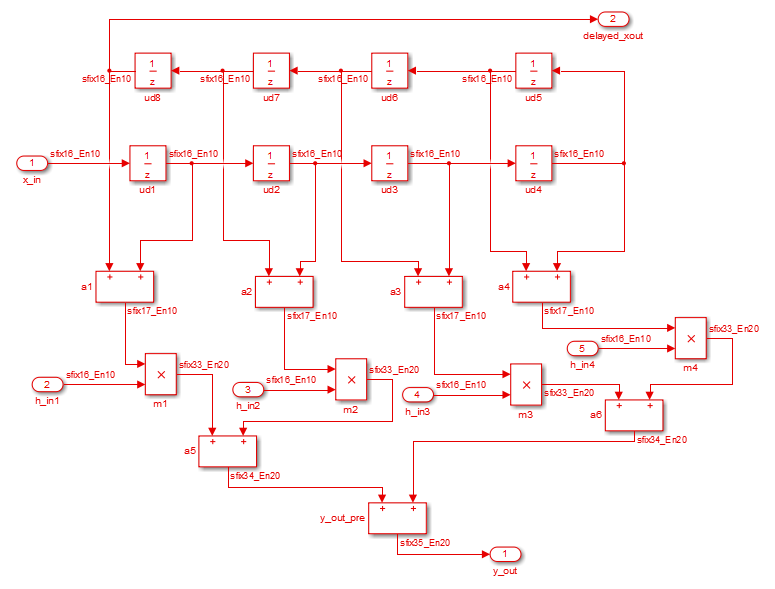

To navigate to the symmetric_fir subsystem,

enter:

open_system('sfir_fixed/symmetric_fir')

Create a Folder and Copy Relevant Files

In MATLAB®:

Create a folder named

sl_hdlcoder_work, for example:mkdir C:\work\sl_hdlcoder_worksl_hdlcoder_workstores a local copy of the example model and folders and generated HDL code. Use a folder location that is not within the MATLAB folder tree.Make the

sl_hdlcoder_workfolder your working folder, for example:cd C:\work\sl_hdlcoder_workSave a local copy of the

sfir_fixedmodel to your current working folder. Leave the model open.

Open HDL Code Generation Pane of Configuration Parameters Dialog Box

To open the HDL Code Generation pane of the Configuration Parameters dialog box, in the Apps gallery, click HDL Coder. The HDL Code tab appears. In the Prepare section, click Settings.

The HDL Code Generation pane consists of basic options that specify the DUT that you want to generate code for, target language, and folder settings. The Generate HDL for setting is synchronized with the Code for menu in the HDL Code tab. You can also use the buttons in this pane to initiate code generation and perform compatibility checking. The HDL Code Generation pane consists of various sub-panes that you can use to specify various settings related to clock and reset signals to reporting and optimization settings.

In the HDL Code Generation pane

The Generate HDL for field specifies the

sfir_fixed/symmetric_firsubsystem for code generation.The Language field specifies generation of VHDL code.

The Folder field specifies a target folder that stores generated code files and scripts.

Generate HDL Code

To generate code, click the Generate button. By default,

HDL Coder™ generates VHDL code in the target hdlsrc

folder.

To generate Verilog code for the model:

In the HDL Code tab, click Settings.

In the HDL Code Generation pane, for Language, select

Verilog. Leave other settings to the default. Click Apply and then click Generate.

HDL Coder compiles the model before generating code. Depending on model display options such as port data types, the model can change in appearance after code generation. As code generation proceeds, HDL Coder displays progress messages in the MATLAB command line with:

Link to the Configuration Set that indicates the model for which the Configuration Parameters are applied.

Links to the generated files. To view the files in the MATLAB Editor, click the links.

symmetric_fir.vhd: VHDL code. This file contains an entity definition and RTL architecture implementing thesymmetric_fir.vhdfilter.symmetric_fir_compile.do: Siemens® ModelSim™ compilation script (vcom command) to compile the generated VHDL code.symmetric_fir_synplify.tcl: Synplify® synthesis script.symmetric_fir_map.txt: This report maps generated entities to the subsystems that generated them. See Trace Code Using the Mapping File

The process completes with the message:

### HDL Code Generation Complete.