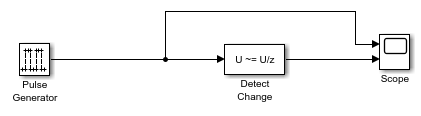

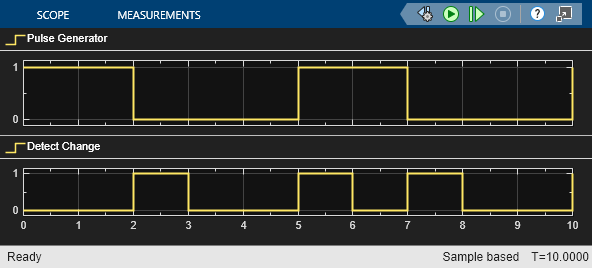

Detect Change

Detectar cambios en el valor de una señal

Bibliotecas:

Simulink /

Logic and Bit Operations

HDL Coder /

Logic and Bit Operations

Descripción

El bloque Detect Change determina si el valor de una señal de entrada no es igual a su valor anterior. La condición inicial determina el valor inicial de la entrada anterior U/z.

Este bloque solo admite tiempos de muestreo discretos de paso fijo.

Ejemplos

Puertos

Entrada

Salida

Parámetros

Características del bloque

Tipos de datos |

|

Paso directo |

|

Señales multidimensionales |

|

Señales de tamaño variable |

|

Detección de cruce por cero |

|

Capacidades ampliadas

Historial de versiones

Introducido antes de R2006a

Consulte también

Detect Decrease | Detect Fall Negative | Detect Fall Nonpositive | Detect Increase | Detect Rise Nonnegative | Detect Rise Positive