Utilizar Simulink Design Verifier para una verificación sistemática de modelos

Los ingenieros de control de los ámbitos aeroespacial y automoción necesitan garantizar que los algoritmos de control subyacentes tengan el comportamiento deseado a lo largo de todo el ciclo de vida operativo.

Simulink® Design Verifier™ permite realizar una verificación sistemática de modelos para identificar errores de diseño ocultos, demostrar propiedades y generar casos de prueba para pruebas funcionales. Simulink Design Verifier utiliza métodos de verificación formales para probar la corrección del diseño e incrementar la confianza en el modelo del diseño que utiliza la generación de código de producción. Por ejemplo, es posible que los ingenieros realicen una verificación y validación durante el ciclo de desarrollo para garantizar que:

El sistema de gestión del motor no da lugar a comportamientos no deseados como una aceleración no deseada o apagado inesperado del motor durante el funcionamiento.

Las aplicaciones de sistemas avanzados de asistencia al conductor (SAAC) que controlan los frenos y volantes funcionan bien bajo cualquier circunstancia.

Los sistemas de piloto automático responden satisfactoriamente a todas las condiciones y entradas de vuelo posibles.

Los sistemas de control de vuelos son estables y activos para evitar fallos catastróficos durante un vuelo.

Un diseñador de modelos y un ingeniero de pruebas usan Simulink Design Verifier a lo largo de la fase de desarrollo del modelo para realizar la verificación y validación.

Prestaciones de Simulink Design Verifier

Simulink Design Verifier ofrece las siguientes funcionalidades:

| Funcionalidad | Descripción |

|---|---|

| Análisis de requisitos funcionales |

Para obtener más información, consulte Use Specification Models for Requirements-Based Testing. |

| Generación de pruebas |

Para obtener más información, consulte Workflow for Test Generation. |

| Detección de errores de diseño |

Para obtener más información, consulte What Is Design Error Detection? |

| Demostración de propiedades |

Para obtener más información, consulte Prove Model Properties |

| Análisis incremental, filtrado y justificación |

|

Análisis de código generado |

|

Certificación o cumplimiento | Permite cumplir los estándares de la industria ISO 26262 para el sector de la automoción o DO-178C para el sector aeroespacial utilizando artefactos generados. |

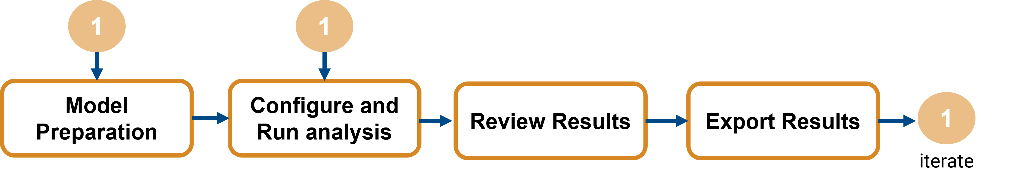

Cómo utilizar Simulink Design Verifier

Usar Simulink Design Verifier incluye los siguientes pasos clave.

Preparar modelo: Prepare el modelo para el análisis.

Seleccione el modo de análisis, como análisis de generación de casos de prueba, análisis de detección de errores de diseño o análisis de demostración de propiedades.

Configure los parámetros del análisis y compruebe la compatibilidad del modelo con el análisis. Para obtener más información, consulte Analyze Model and Interpret Results.

Configurar ajustes del modelo y ejecutar análisis: Especifique la configuración del modelo y realice el análisis relevante para sus necesidades de análisis.

Seleccione el tiempo máximo de análisis, modo de cobertura, modo de error en tiempo de ejecución, estrategia y otros parámetros de configuración para el análisis.

Ejecute el análisis.

Revisar resultados: Vea los resultados generados.

Una vez finalizado el análisis, inspeccione los resultados resaltados del modelo con Simulink Design Verifier.

Revise el estado de los objetivos y defina las acciones de seguimiento.

Genere el informe del análisis.

Exportar resultados: Utilice la información obtenida de los resultados para ajustar la configuración del modelo o análisis.

Cree un arnés para la simulación.

Exporte los casos de prueba a Simulink Test™.

Para obtener más información, consulte Analyze Model and Interpret Results.

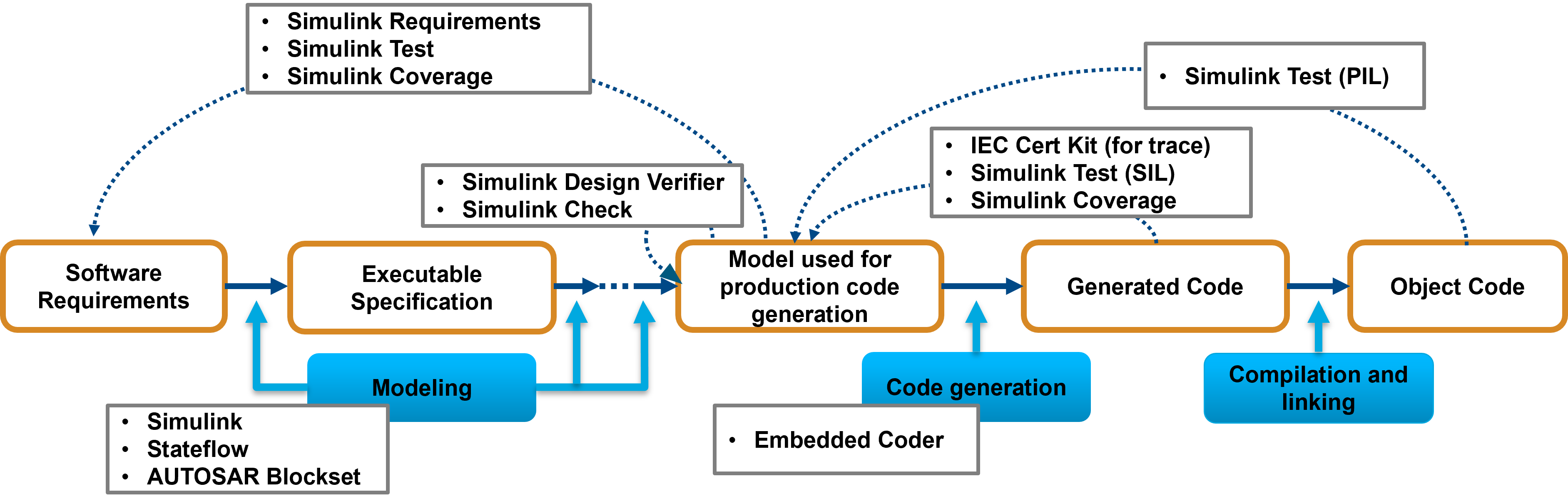

Simulink Design Verifier en diseño basado en modelos

Esta figura ilustra las prestaciones de Simulink Design Verifier en distintas fases del flujo de verificación y validación.

Con Simulink Design Verifier, puede:

Identificar errores de diseño ocultos, como desbordamientos de enteros o división por cero, y generar contraejemplos para depurar funcionalidades no deseadas. También se pueden justificar o excluir objetos modelo del análisis.

Comprobar el modelo en base a requisitos utilizando Requirements Toolbox™.

Completar la cobertura del modelo (Simulink Coverage) generando casos de prueba que cumplan los objetivos de cobertura del modelo.

Realizar análisis de cobertura de código (Embedded Coder) generando casos de prueba para código generado por Embedded Coder®.

Ampliar casos de prueba existentes y resolver deficiencia de cobertura.

Integrar casos de prueba con Simulink Test para realizar pruebas de referencia y equivalencia.

Cumplir con estándares de la industria a través de IEC Certification Kit (for IEC 61508 and ISO 26262) y DO Qualification Kit (for DO-178).

Con Simulink Design Verifier también puede cumplir con estándares de la industria a través de IEC Certification Kit (for IEC 61508 and ISO 26262) y DO Qualification Kit (for DO-178).