Esta página fue traducida automáticamente.

Complete una encuesta de 1 minuto sobre la calidad de esta traducción.

Rambus desarrolla bloques de DSP para ASIC empleando síntesis de alto nivel con HDL Coder

“Por lo general, los equipos de verificación y back-end no pueden comenzar la integración hasta que esté lista la primera versión de RTL basado en especificaciones, que aún pueden tener errores. Con este flujo de trabajo basado en HDL Coder, se puede generar HDL a partir de un modelo verificado en nivel de sistema con solo un clic, ahorrando meses de trabajo y garantizando un punto de partida de alta calidad para estos equipos”.

Resultados principales

- El proceso de diseño se aceleró de un año a tres meses y la productividad aumentó utilizando generación de código HDL, con un 80 % del código generado retenido en la implementación final

- El desarrollo del entorno de verificación comenzó con el código RTL generado automáticamente y continuó en paralelo con el desarrollo RTL personalizado

- Pasar de una generación de diseño a otra o de implementaciones de la misma generación requirió cambios limitados en el modelo de Simulink compatible con HDL

Los dispositivos de comunicación actuales incorporan algoritmos de procesamiento de señales complejos implementados en circuitos integrados para aplicaciones específicas (ASIC) para lograr mayor rendimiento, menor costo del producto final y menor consumo de energía. El proceso de implementación física de ASIC es largo. Comienza antes de que se complete la verificación de RTL y requiere integración manual de sumadores y multiplicadores optimizados, así como funciones de depuración y observabilidad RTL.

Ehud Nir, director de ingeniería digital en Rambus, necesitaba desarrollar DSP para un PHY PCIe Gen6 con tiempo y recursos de ingeniería limitados. Un proyecto anterior con diseño comparable requería que un diseñador ASIC desarrollara código RTL y a un ingeniero de verificación elaborara bancos de pruebas durante 12 meses. Dado que el arquitecto del sistema había utilizado MATLAB® y Simulink® para modelar el serializador/deserializador Gen6 completo (SerDes) y el DSP, Ehud decidió acelerar el proceso de diseño utilizando HDL Coder™ para generar una referencia RTL para la implementación ASIC directamente a partir del modelo de Simulink.

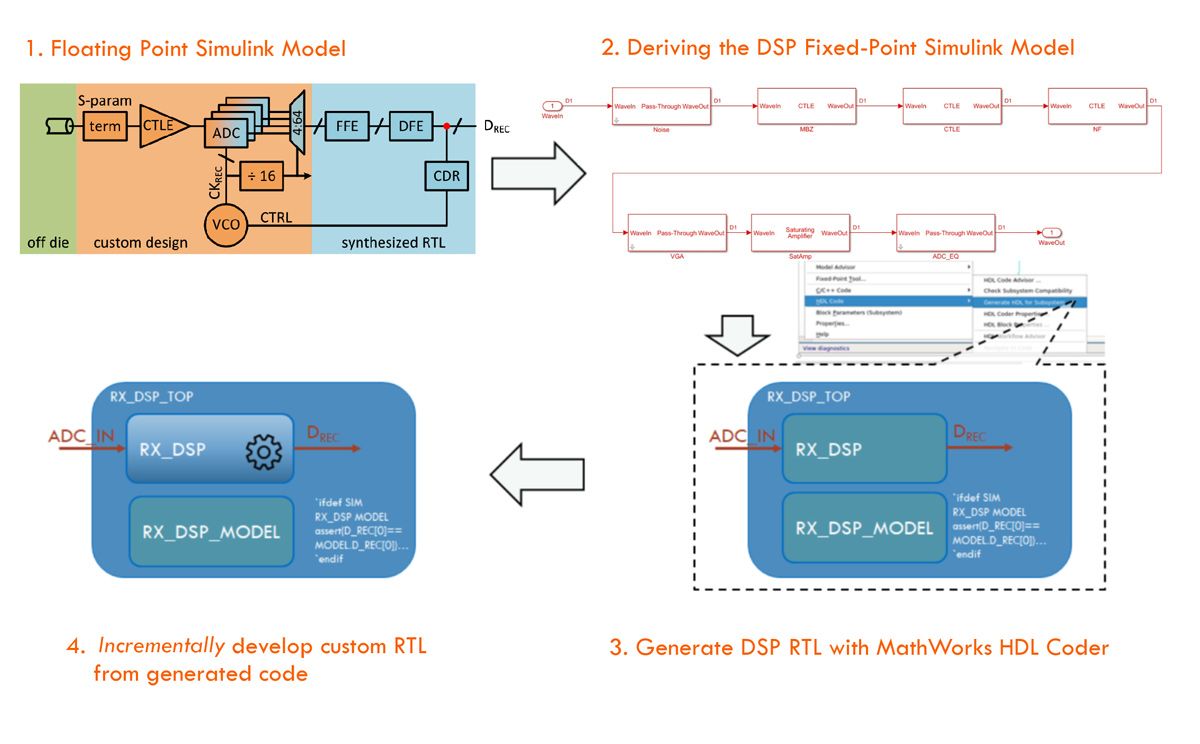

Para comenzar, el arquitecto del sistema convirtió el modelo de Simulink de punto flotante del DSP SerDes a punto fijo. Después de garantizar que este modelo cumplía con las especificaciones y características eléctricas objetivo, un diseñador digital ASIC generó código RTL a partir del modelo de punto fijo utilizando HDL Coder. Este modelo de referencia se regeneró desde Simulink varias veces durante el proceso de diseño debido a la evolución de los requisitos, como las modificaciones al filtro frontal digital.

El código RTL generado por HDL Coder sirvió como punto de referencia para que el equipo de verificación comenzara la verificación en nivel de IP y los equipos back-end comenzaran el diseño físico. Mientras tanto, el diseñador digital personalizó el código RTL desarrollando la lógica combinatoria y secuencial para reducir el consumo de energía y agregar modos de bajo consumo. El uso del RTL generado como referencia permitió realizar una comparación jerárquica completa entre el RTL personalizado y la referencia RTL generada. Con afirmaciones agregadas, el RTL personalizado se puede verificar usando simuladores HDL para garantizar su precisión en términos de ciclo de bits respecto del modelo de referencia. Como resultado, un solo ingeniero pudo producir una lista de conexiones DSP completamente verificada y libre de problemas de temporización en menos de tres meses, en comparación con dos ingenieros trabajando 12 meses en el proyecto anterior. El chip de prueba Gen6 PHY ASIC impulsado por este DSP fue validado en el laboratorio con éxito en el primer intento.

Productos utilizados