Generate Custom Timing Database for Custom Tools and Devices

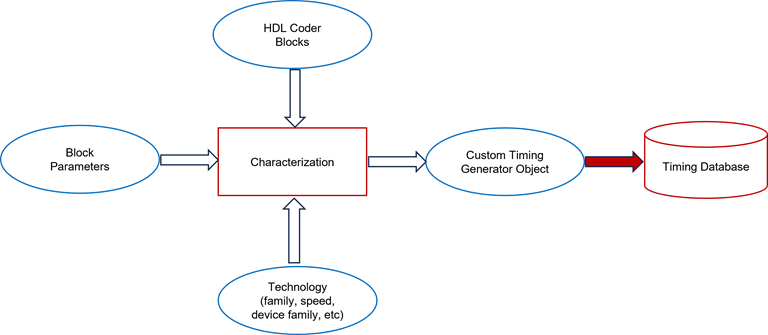

To generate a custom timing database for tools and devices, HDL Coder™ uses the characterization of basic design components, such as Simulink® blocks, block architectures, and subcomponents of those blocks, for

specific target devices and passes this information to a

hdlcoder.TimingGenerator object. The

hdlcoder.TimingGenerator object generates a timing information

file with static timing information. The genhdltdb function uses

the timing information file to generate a custom timing database.

You can generate a timing generator object by using the

hdlcoder.TimingGenerator handle class. HDL Coder includes timing generator objects for Cadence® Genus, Intel®

Quartus®, Xilinx®

Vivado®, and Microchip Libero® SoC that you can use to create a custom timing generator for your tool or

device. For more information, see hdlcoder.TimingGenerator.

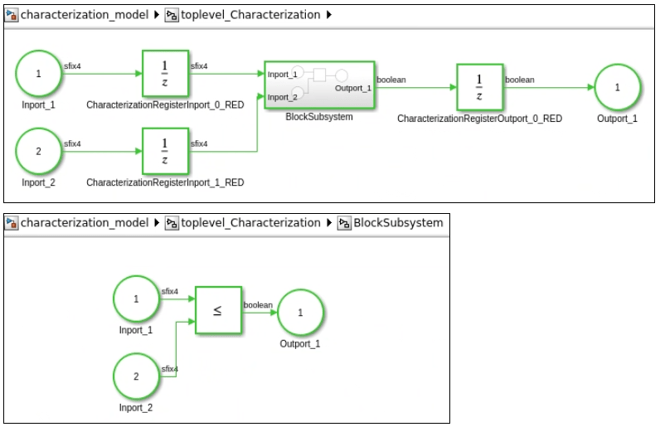

The timing generator object outputs a comma-separated value (CSV) text file that contains the propagation delays in nanoseconds (ns). For example, suppose you use the model in this image

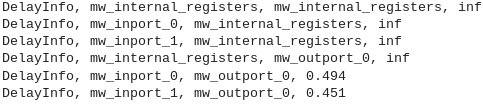

The timing generator outputs this CSV text file:

The file contains information in this format: DelayInfo, source_type,

destination_type, propagation delay (ns).

The source_type or destination_type fields are

of type:

mw_internal_registers— Any internal register inside the subsystem that contains the block to be characterized.mw_inport_#— Numbered input to the operator starting at index zero. For example,mw_inport_0,mw_inport_1, and so on.mw_outport_#— Numbered output from the operator starting at index zero. For example,mw_outport_0,mw_outport_1, and so on.propagation delay (ns)— The value in nanoseconds for either internal-to-internal, input-to-internal, internal-to-output, or input-to-output propagation delay. If a timing path does not exist, this value isinf. This field contains the timing information for every path.

hdlcoder.TimingGenerator Method Options

Since R2024b

Perform synthesis and timing analysis for a custom device using any tool, by

creating a custom hdlcoder.TimingGenerator class. To create a custom

timing class:

Create a custom

hdlcoder.TimingGeneratorclass that inherits from the basehdlcoder.TimingGeneratorclass.Define methods inside the custom

hdlcoder.TimingGeneratorclass to perform actions such as generating or calling TCL scripts that create projects, perform synthesis, perform timing analysis, remove setup and clock-to-Q delays from timing reports, and so on.

For an example on creating a custom timing generator class, see Examine Xilinx Vivado Custom Timing Generator Class. This table

lists the methods that you can define in a custom timing class. You must define the

synthesizeRTL and hasDSPs methods. If you set

the hasDSPs method to true, you must define the

countDSPs, dspSynthesisAttribute, and

dontTouchSynthesisAttribute methods. If your device does not

have DSPs or you do not want to characterize your DSPs, set hasDSPs

to false.

| Method Name | Purpose | Inputs | Outputs | Method Definition Required |

synthesizeRTL | Generate or call TCL scripts that create projects, perform synthesis, and perform timing analysis. | hdlcoder.TimingGenerator object | Status of the method returned as a logical

data type and a log text. | Yes |

postProcessTimingInfo | Remove setup and clock-to-Q delays from timing reports. | hdlcoder.TimingGenerator object and a

MATLAB® structure array containing timing information. | MATLAB structure array that contains timing information. | No |

useSynchronousReset | Tell HDL Coder what to set the global resets to. | No inputs | true or false. If the

method returns true, generate synchronous

resets. If the method returns false, generate

asynchronous resets. | No |

hasDSPs | Enable characterization of device DSPs. | No inputs | Returns true if the manufacturer uses

DSPs. | Yes |

countDSPs | Return the number of DSPs found during synthesis. | Synthesis log text | Returns the number of DSPs counted during synthesis | Yes, if hasDSPs is

true. |

dspSynthesisAttribute | Force multipliers to map to DSPs. | No inputs | Returns a cell array of synthesis attribute name-value arguments to use during HDL code generation. | Yes, if hasDSPs is

true. |

dontTouchSynthesisAttribute | Prevent optimization of signals connected to input and output pipeline registers during synthesis. | No inputs | Returns a cell array of synthesis attribute name-value arguments to use during HDL code generation. | Yes, if hasDSPs is

true. |

See Also

hdlcoder.FloatingPointTargetConfig | makehdl | genhdltdb | hdlcoder.TimingGenerator