Efficient Fixed-Point Implementation of a Filter on an FPGA

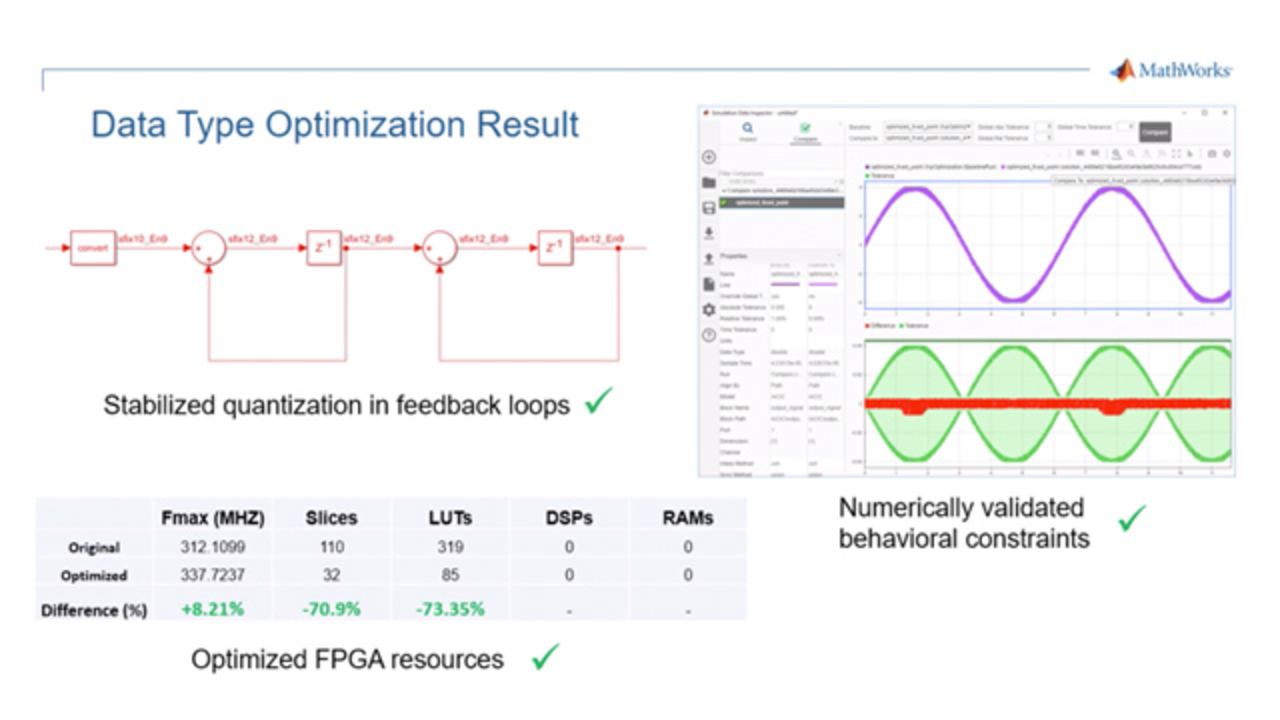

The data type optimization feature in Fixed-Point Designer™ enables you to automatically iterate to find optimal data types for efficient implementation on an FPGA while meeting constraints on the numerical behavior of your system.

Starting from a 32-bit fixed-point implementation of a CIC filter, see how data type optimization lets you convert to a more efficient implementation. Using no more than 12 bits, you have a stable CIC filter with the quantization noise within budget. The resulting implementation on a Xilinx® Virtex® 7 FPGA uses significantly less resources particularly the LUT and logic slices.

Published: 14 Jun 2018