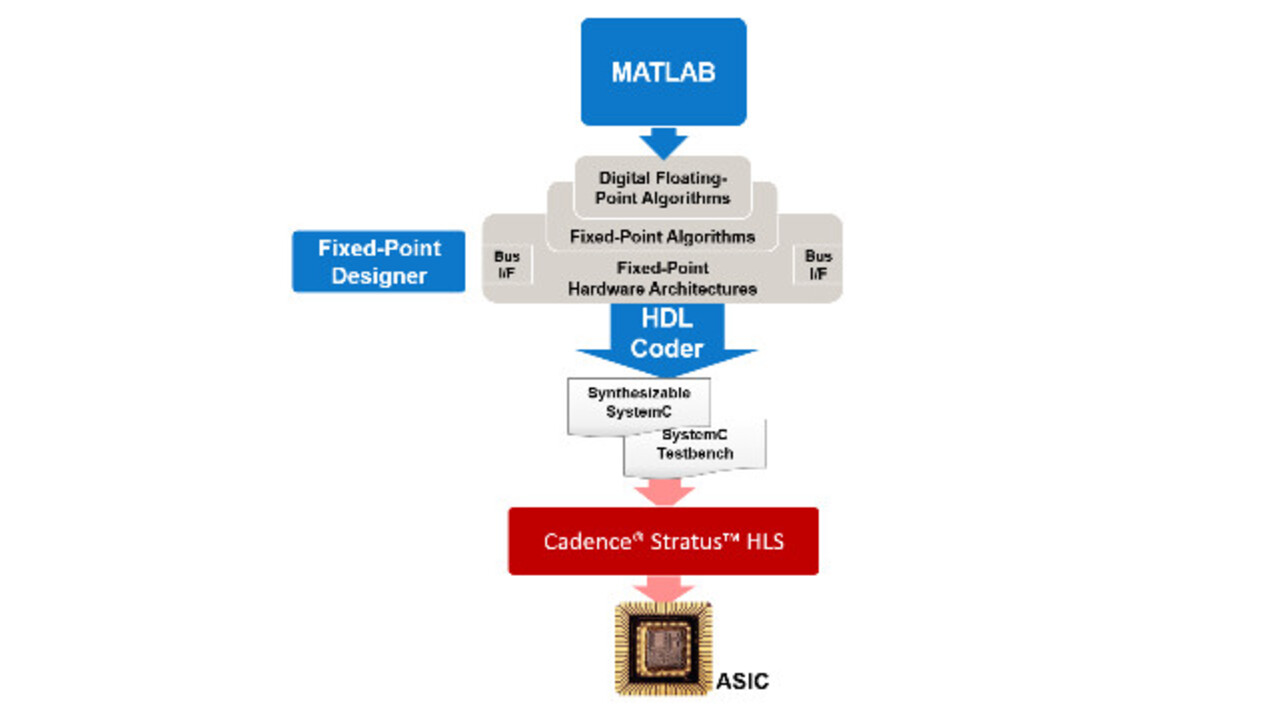

MATLAB-to-SystemC Workflow for Cadence Stratus HLS

Watch a step-by-step demonstration of how to use HDL Coder™ with the Cadence® Stratus™ HLS high-level synthesis tool to create highly optimized ASIC implementations of MATLAB® code. The demo features a floating-point, least-mean squares (LMS) digital filter in MATLAB. The HDL Coder workflow is used to generate fixed-point MATLAB code, from which HDL Coder can generate synthesizable SystemC™ code along with a SystemC testbench. Then Stratus HLS is used to verify the System code, synthesize RTL code, and explore alternative ASIC implementations.

Published: 25 Apr 2023

HDL Coder generates Verilog and VHDL RTL code from algorithms modeled in MATLAB and Simulink for implementation in FPGAs and ASICs. Recently HDL Coder has been enhanced to generate synthesizeable SystemC code from MATLAB so that it can be used in combination with high-level synthesis tools.

In this video, we will run through an example of using HDL Coder to prepare a MATLAB function for SystemC code generation, so that can be synthesized to hardware using the Stratus HLS tool from Cadence.

Here’s our MATLAB session. We start with the design to be synthesized – it’s represented here as a MATLAB function but it’s an LMS filter, or least-mean squares filter. It’s a type of adaptive filter, and we’re using it here to remove noise from an audio signal.

The top-level MATLAB function calculates the optimal filter coefficients to reduce the difference between the output signal and the desired signal.

The top-level function calls three other functions, so this is a hierarchical MATLAB function.

The testbench is a MATLAB script that does some setup, creates a sinusoid signal and adds noise to it.

The calls to the top-level function to be synthesize are in this while loop, and once all inputs have been processed the testbench plots the results.

We run the testbench to simulate, and you can see that after just two cycles the filter is starting to remove noise.

Before proceeding, we need to make sure that Stratus is on the tool path, so we run hdlsetuphlstoolpath

We create an HDL Coder project, which includes the function to be synthesized and its testbench.

Once we do that, we can start the HDL Workflow Advisor for MATLAB, which gives us a step-by-step process

To start, we set the Code Generation Workflow. It defaults to the MATLAB to HDL workflow, but we change it to MATLAB to SystemC to take advantage of Stratus and its integration with power analysis and logic synthesis tools.

In the next step, we will define the data types of the four inputs to the MATLAB function. HDL Coder evaluates the function and testbench to infer datatypes on the four inputs to the function as shown here.

The next step deals with Floating-point to fixed-point conversion. This will convert the floating-point MATLAB code to fixed-point MATLAB. HDL Coder performs a range analysis based on simulation of the testbench, and proposes appropriate fixed-point types for each variable in the MATLAB algorithm. You can edit these datatypes and override the proposed values if you’d like to add in more margin.

You can respond that you’re satisfied with the datatypes by clicking on Validate Types. Then HDL Coder generates the fixed-point MATLAB code. This can take some time, so we’ll skip ahead.

In the next step, you can specify Cadence Stratus HLS as the synthesis tool.

Then we move on to the next step, SystemC code generation. You have some options here involving coding style, optimizations, and thresholds on RAM mapping that you can choose from. Once those are set, you Run this step. HDL Coder will report back on progress and notify you when code generation is completed.

Now we can look at the generated SystemC code. The persistent variables in MATLAB that are used to maintain state are generated as public class members. If the size of a persistent variable exceeds the RAM threshold set in the Optimizations tab then it maps to RAM.

We can scroll down and see the SystemC code representing the LMS filter algorithm. As we saw earlier, there are four inputs and three outputs. The outputs are passed by reference.

Now We can return to the Workflow Advisor to verify the SystemC. In this case, we are generating the input/output data from the MATLAB design. We will then create a Stratus project with the generated SystemC. We run a simulation of the SystemC code to verify that it provides the same results as the MATLAB code.

We see the transcript here as we generate the data files and run an importer tool for Stratus. We can skip ahead as this can take time to run. The successful result here means that the SystemC is numerically correct.

At this point, you can launch Stratus by clicking on the link to the Stratus project. This will bring up the Stratus IDE

We can return to Workflow Advisor to kick off synthesis with Stratus, or you can do this within the Stratus IDE. This will produce reports and generate RTL from Stratus. From here on you can proceed with the options Stratus has for further design exploration

For more information on this workflow and other features, go to mathworks.com/hdl, where you can learn more about HDL Coder and its use in ASIC workflows